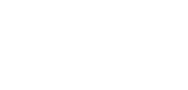

真是岁月如梭啊,到瑞典已经半年光景。在这半年中学习、思考了很多。尤其是对片上网络这个研究领域,很多观念上的认识上有了非常深的转变。赫然间发现以前有很多模糊的错误的概念。从今天开始起陆续发表一系列的文章和各位分享一下心得体会,欢迎各位批评指正和讨论。 多年前,当读到我现在的合作导师Axel Janstch所编著的具有划时代的意义的——《Networks on Chip》(中文翻译为《网络化芯片》,当然我读的是中文。时至今日这本书应该也是为数不多的被翻译成英文的片上网络相关书籍)时,看到书中间有这么段话(大意,原文记不住了):计算机体系结构的设计者和SoC的研究者在片上网络的这一领域找到了交集。之前我看到这句话很是不理解,也没有当一回事。但是现在仔细想来,这句话很有深度。作为一本在10年前出版的书籍,它其实指明了未来搞NoC的会是两拨人:一拨人是自顶而下的,从原来搞并行机出身,把并行机的那套玩意换个载体搬到芯片上面来实现。而另外一拨是自底而上的,是原来从ASIC/SoC设计的这波搞集成电路的人,为了解决ASIC/SoC里面越来越复杂的互联线结构而推动由模块之间的直接互联改为采用片上网络这种方式来互联。这两拨人都不约而同的采用了片上网络作为解决片上数据传输的方案,但二者的出发点和面向的应用却是非常不同的,因而也导致了不同的研究路线。前者的研究逐渐演化成了NoC based 的CMP-chip multiprocessor, 片上多处理器结构。而后者则演化成了NoC based MPSoC-片上多核处理器(我觉得这个中文翻译相当的不好,但是还没有想出更好的)。 CMP是由并行机中的SMP结构发展而来的,其基本的特点是依靠共享内存来实现数据的同步,同样也依靠共享内存来实现数据的交互。计算机体系结构的研究者在这一领域耕耘多年,在这一领域具备得天独厚的优势。其原因是整个计算机学科很早就确立了基于存储的计算模式,对于这套以存储为中心进行数据交换的模式得心应手。在没有在片上实现多处理器的时代,计算机体系结构的设计者早已经通过各种高速专用互联网络实现了多个处理节点和共享存储单元之间的互联。看看下图:

看到了没有,左边是国内各种教材讲并行计算用的SMP模型,右边是提出的一种64Bank的NoC based的CMP架构。这两个玩意根本就是一回事好吧……只不过就是把原来在板级或者是机柜级用高速交换开关或专用网络互连的memory变成了用片上网络来互连L2 cache了。当然,这只是NoC based的CMP其中一种架构。但其它各种类似的架构都会在原来的并行机中找到的对应的原型,比如DSM-虚拟分布共享存储什么的。

其实对于CMP而言, 基于NoC并不是一直很好的互连形式。因为CMP依赖于存储器进行数据同步,因此必须有一套保证存储器中数据一致的协议,被称为CC(cache coherence)协议。这套协议的核心是有赖于广播某个cache中的数据已经被修改的信息,从而让其它cache中的那个旧数据失效,从而保证旧的数据不会参与到运算中而导致结果错误。对于network而言,广播是一个费时费力的事情。而对于总线来说,广播就是一个天然的事情。因为总线天生就是一个广播信道。所以目前还有很多论文在讨论混合式的NoC,通常都是在NoC之外专门又为数据加一条广播总线什么的。

说完了CMP,回头又来说说MPSoC.其实一开始我也是被MPSoC这个名词所误导,好像MPSoC使用NoC是为了互联多个处理器的。其实这个理解就过于狭隘了。我们首先来追溯一下怎么从ASIC/SoC设计开始搞到NoC 。

随着现代的ASIC设计规模越来越大,后端的布局布线其实遇到了很大的挑战。因此后端物理设计的时候就开始推出一种叫Hierarchical Physical Implementation Flow 的方法。其实就是把整个芯片划分成若干个子模块,分别进行自动布局布线。在此基础上再将各个子模块之间相互连接,构成一个完整的Chip.但是问题又来了,如果这些模块足够多的时候,他们之间的互联也是需要解决的问题。

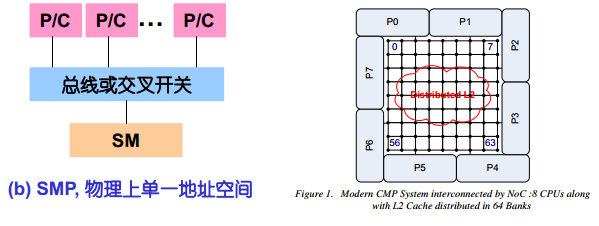

下图就给了一个很好的NoC based的chip互联的例子。

看到了没有,左边是国内各种教材讲并行计算用的SMP模型,右边是提出的一种64Bank的NoC based的CMP架构。这两个玩意根本就是一回事好吧……只不过就是把原来在板级或者是机柜级用高速交换开关或专用网络互连的memory变成了用片上网络来互连L2 cache了。当然,这只是NoC based的CMP其中一种架构。但其它各种类似的架构都会在原来的并行机中找到的对应的原型,比如DSM-虚拟分布共享存储什么的。

其实对于CMP而言, 基于NoC并不是一直很好的互连形式。因为CMP依赖于存储器进行数据同步,因此必须有一套保证存储器中数据一致的协议,被称为CC(cache coherence)协议。这套协议的核心是有赖于广播某个cache中的数据已经被修改的信息,从而让其它cache中的那个旧数据失效,从而保证旧的数据不会参与到运算中而导致结果错误。对于network而言,广播是一个费时费力的事情。而对于总线来说,广播就是一个天然的事情。因为总线天生就是一个广播信道。所以目前还有很多论文在讨论混合式的NoC,通常都是在NoC之外专门又为数据加一条广播总线什么的。

说完了CMP,回头又来说说MPSoC.其实一开始我也是被MPSoC这个名词所误导,好像MPSoC使用NoC是为了互联多个处理器的。其实这个理解就过于狭隘了。我们首先来追溯一下怎么从ASIC/SoC设计开始搞到NoC 。

随着现代的ASIC设计规模越来越大,后端的布局布线其实遇到了很大的挑战。因此后端物理设计的时候就开始推出一种叫Hierarchical Physical Implementation Flow 的方法。其实就是把整个芯片划分成若干个子模块,分别进行自动布局布线。在此基础上再将各个子模块之间相互连接,构成一个完整的Chip.但是问题又来了,如果这些模块足够多的时候,他们之间的互联也是需要解决的问题。

下图就给了一个很好的NoC based的chip互联的例子。

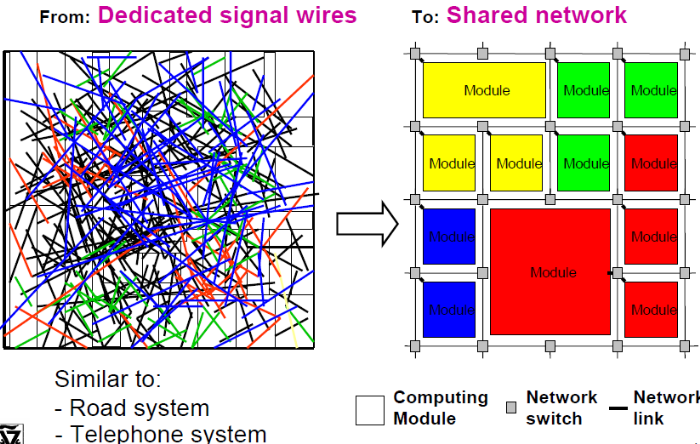

各位看出来了吧,这套NoC的用法就和上面的CMP的用法有着本质的区别。可以说是原来ASIC/SoC设计的一个变种。那么如果说这玩意还有点抽象的话呢,那么晚我再上一个图,给一个简单的例子。可重构的无线基带处理器:

各位看出来了吧,这套NoC的用法就和上面的CMP的用法有着本质的区别。可以说是原来ASIC/SoC设计的一个变种。那么如果说这玩意还有点抽象的话呢,那么晚我再上一个图,给一个简单的例子。可重构的无线基带处理器:

看到这张图的时候,哥突然有种醍醐灌顶外加泪流满面的感觉。这么多年苦苦寻求的用于通信的可重构处理器,其实就是这个样子的……同时兼容了wifi,wimax和DVB的基带处理器~~~虽然我觉得这个设计也不是特别好。

呵呵,不是特别好是吧?那么就来几张特别好的……(静待下期,O(∩_∩)O~)

看到这张图的时候,哥突然有种醍醐灌顶外加泪流满面的感觉。这么多年苦苦寻求的用于通信的可重构处理器,其实就是这个样子的……同时兼容了wifi,wimax和DVB的基带处理器~~~虽然我觉得这个设计也不是特别好。

呵呵,不是特别好是吧?那么就来几张特别好的……(静待下期,O(∩_∩)O~)