长期以来,很多朋友搞不太清楚FPGA设计(严格意义上讲应该叫“基于FPGA的数字系统设计”)和ASIC设计(严格意义上讲应该叫“用半定制设计方法去设计ASIC”)之间太多区别。总觉得都是用Verilog写写代码,然后放进工具里面跑一跑。好像没有什么不同。

再稍微懂行一点的呢就会说:FPGA嘛,直接出来一堆二进制文件然后下载到开发板里就可以用了;ASIC呢,还需要做一堆后端的工作才行。其实现在FPGA设计方和ASIC设计方法已经差别非常大了,但是很多人并没有意识到。即便是很多做“数字集成电路”方面的研究者和业界的从业人员都没有刻意思考过这个问题。这个话题要是放开了讲,可以写一系列的专栏文章。今天这文章的目的不是这个,所以改日再来谈这个话题。

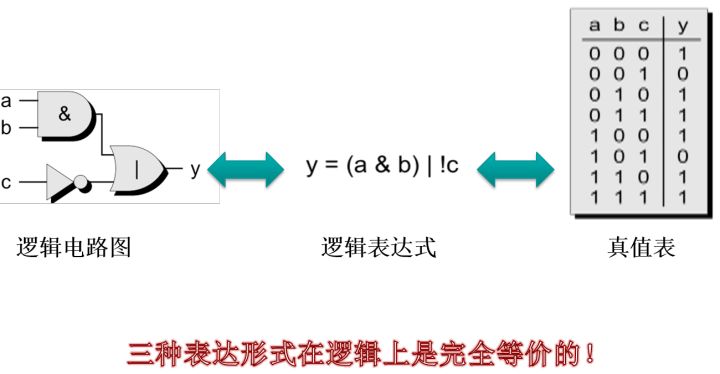

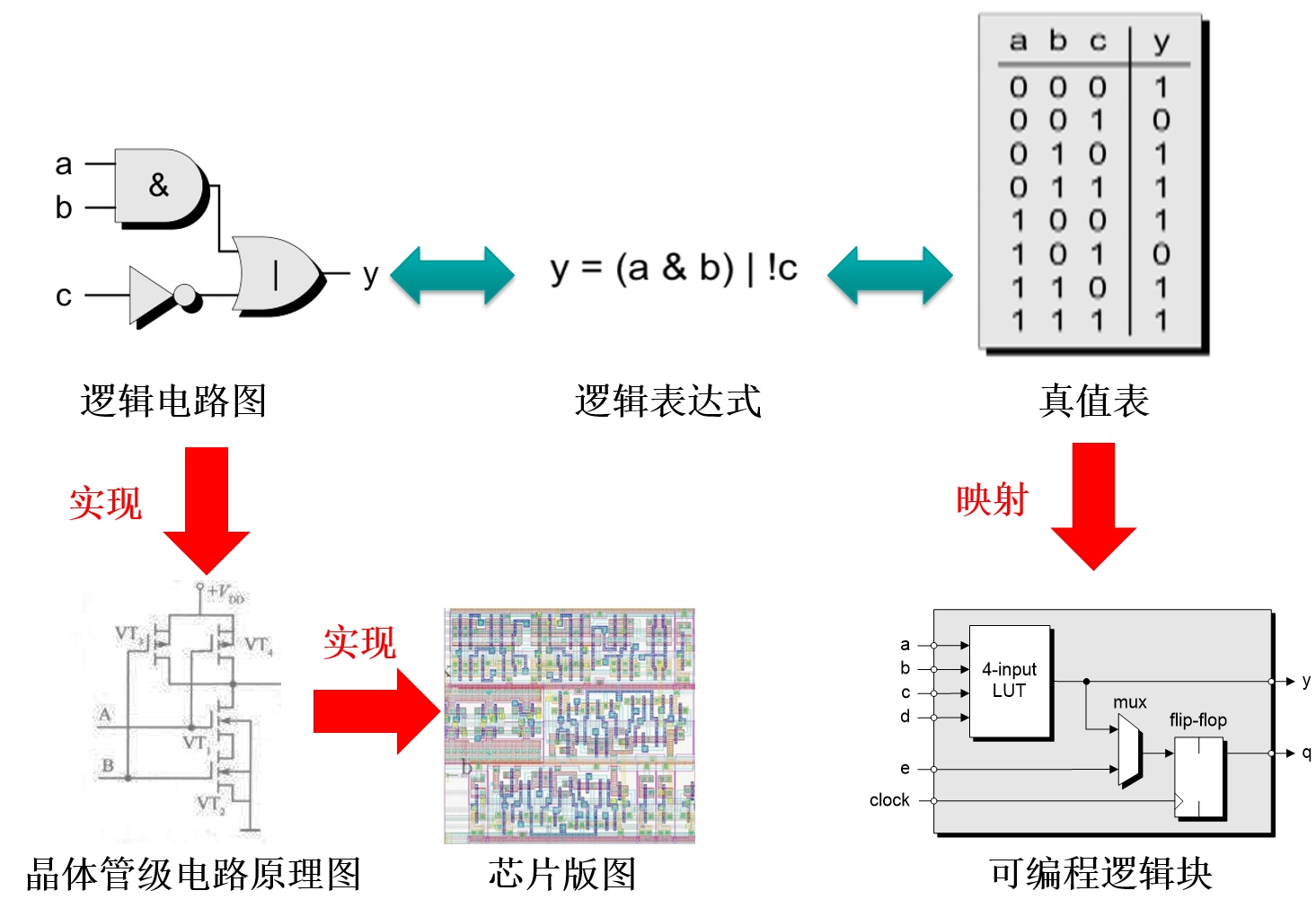

逻辑电路图、逻辑表达式和真值表三者在逻辑上是等价的。这种等价的意义何在呢?因为数字电路/数字系统的理论基础就是布尔逻辑。无论是ASIC形式的数字集成电路也好,还是基于FPGA的设计也好,在绝大部分时候就是在实现各种逻辑表达式。因此任何有能力实现逻辑表达式的方式仅从功能上来说都是等价的。

也就是会得到下面这个结果:

逻辑电路图可以进一步细化为晶体管级的电路原理图,而晶体管级的电路原理图经过物理设计又会得到可以用于去加工制造的芯片版图。如果把这个芯片加工出来,这最红得到的版图就是对应的逻辑电路图的功能,也就是对应了想实现的逻辑表达式。把真值表映射到一个FPGA内部的可编程逻辑块,通过确定输入输出关系通用也可以实现相同的逻辑表达式。

当然了,我们不会去手动去实现这个逻辑表达式,我们甚至都不会去亲自去得到这个逻辑表达式。在电子设计自动化工具已经高度发达,数字集成电路设计方法学已经足够完善的今天。我们基本都是靠输入一段硬件描述语言代码之后,操作各种工具来得到最后的实现形式。现在我们甚至可以用高级语言或者图形化界面去生成一段硬件描述语言或者直接通过图形化的操作得到最后的逻辑表达式。

那现在就有很多问题了。

1.在电子设计自动化工具如此发达的今天,做数字集成电路设计到底是在干什么?

2.数字集成电路设计的核心是“写代码”吗?

3.学习数字集成电路设计的重点是在“操作工具”吗?

4.如果是依靠写代码+操作工作设计自动化工具,那么学习半导体器件、量子力学、微电子技术的意义还大吗?

5.现行微电子专业的培养模式下教育出来的学生从事数字集成电路设计,尤其是前端设计的优势有吗?

……

要回答这些问题,不得不回到一个根本性的命题上面来:“到底什么叫数字集成电路设计,数字集成电路设计的核心到底在哪里”?其实我开这个Live也是试图回答这个问题。在过去的很多年中我总是被称为“做数字”的老师。无论是学生还是我们学院的其他老师,甚至是同组的其他老师,他们普遍都有这样一个问题:说起来,你应该是“做数字的”,但是你做的这种“数字集成电路”怎么和我们通常理解的不一样呢?被问烦了以后,我也就想到了这个办法:干脆我就来做一场“你可能学了假的数字集成电路”的Live算了。

今天先谈到这里,更多预告内容将持续更新。